cache写回法 verilog实现_Gvim是最好用的Verilog代码编辑器

标题党!标题党!工具没有最好,只有最适合你的,Verilog行为级描述虽然已经抽象了很多,但是对于大规模的电路设计,Verilog有很多冗余编码逻辑,比如自动定义,自动实例化等等,尤其是做Top集成,上万行的连线,手动连线十分低效,也容易出错。比如现在很多工具上都有提高Verilog代码编写效率的插件,本文是分享的是两个Gvim的自动化插件。我一直有疑惑,这个人用Vim还邦邦的敲鼠标两个...

·

标题党!标题党!工具没有最好,只有最适合你的,Verilog行为级描述虽然已经抽象了很多,但是对于大规模的电路设计,Verilog有很多冗余编码逻辑,比如自动定义,自动实例化等等,尤其是做Top集成,上万行的连线,手动连线十分低效,也容易出错。比如现在很多工具上都有提高Verilog代码编写效率的插件,本文是分享的是两个Gvim的自动化插件。

我一直有疑惑,这个人用Vim还邦邦的敲鼠标

我一直有疑惑,这个人用Vim还邦邦的敲鼠标

两个插件

为了高效的编写Verilog,通常有些编辑器插件可以自动生成代码,比如自动端口定义,自动连线,自动实例化等等。一般的公司的环境有很好用的自动化插件,想给自己的电脑也整个怎么做。博主找到了两个插件- Emacs中有个插件叫verilog-mode。博主习惯了用Vim,查询后发现Vim也可以调用这个插件来实现自动化。verilog-mode开发者网站在这里,更多内容去上网查询。https://www.veripool.org/wiki/verilog-mode

- vim官网上也有一个插件,作者zhang guo,有好用的autodefine功能,这两个可以配合着用,写代码的时候可以完全不用在意reg和wire类型的定义,直接写assign和always块,最后autodefine一下就可以了。https://www.vim.org/scripts/script.php?script_id=4067

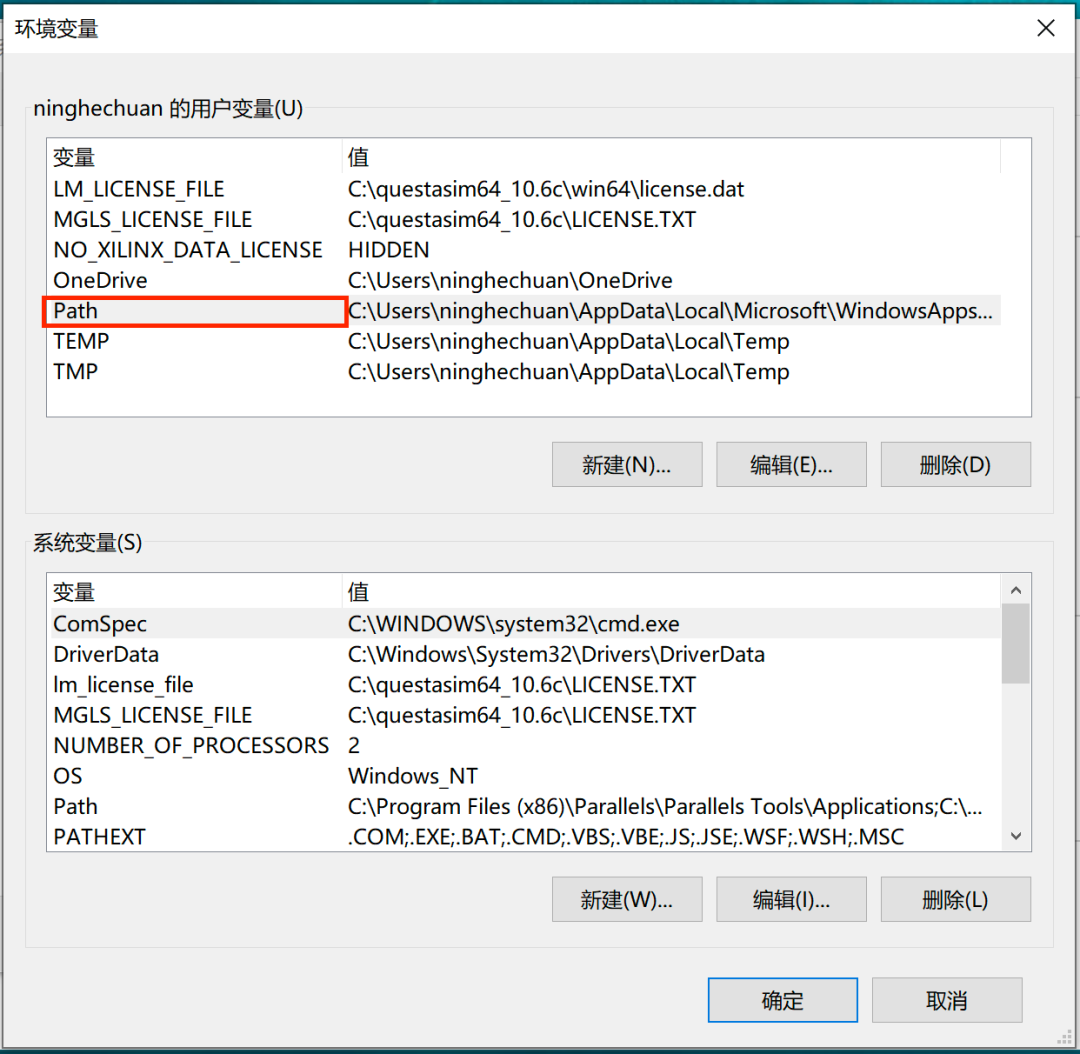

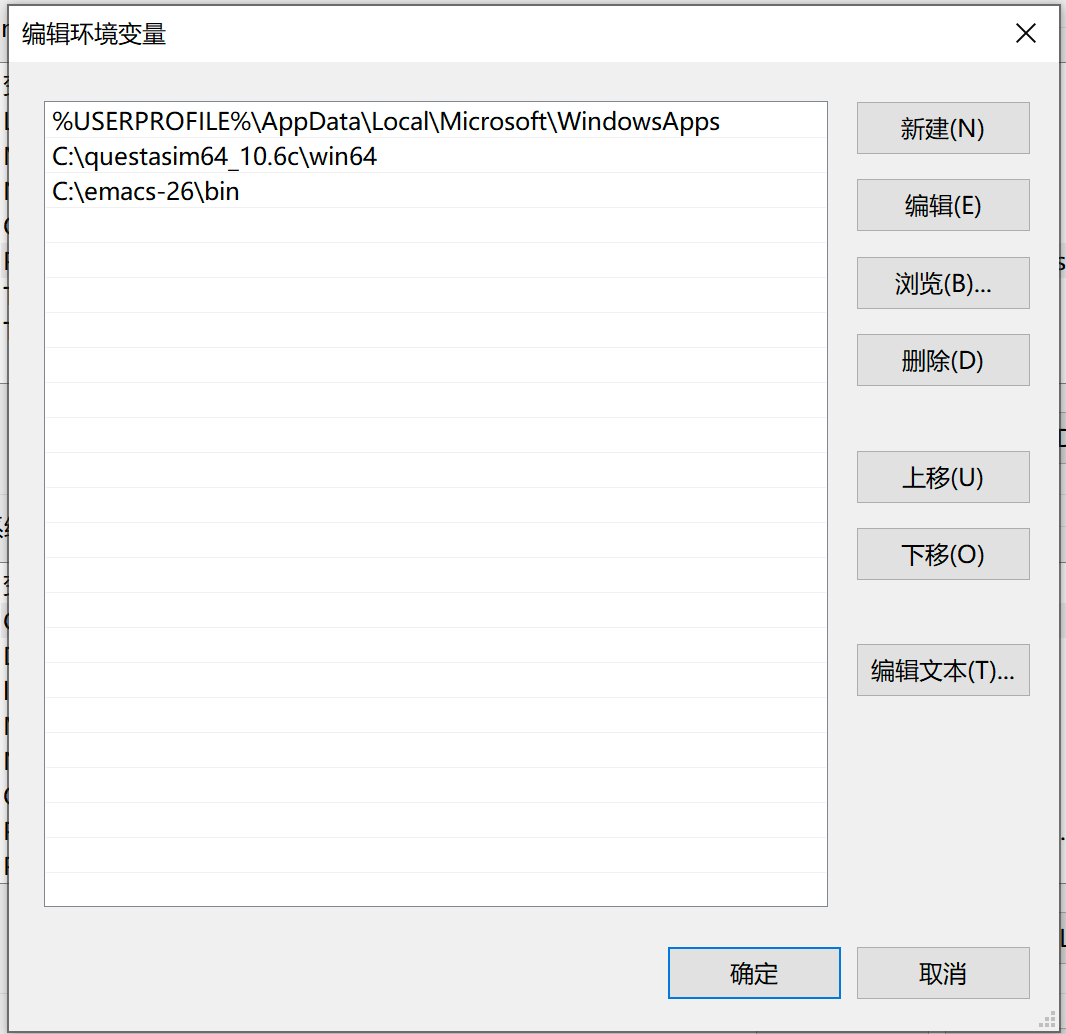

Emacs的配置使用

自动化前module test (/*AUTOARG*/);input clk;input rst_n; input i;output douty;parameter DWIDTH=32;/*AUTOREG*//*AUTOWIRE*/assign doutx = i;always @(posedge clk or negedge rst_n)begin if(!rst_n)begin douty <= 1'd0; end else douty <= doutx;endassign doutx = i & o[DWODTH-1];foo u_foo(/*autoinst*/);endmodule//Local Variables://verilog-library-directories:("." "foo")//End:module foo(/*AUTOARG*/);input i;output [DWIDTH-1:0] o;endmodule//Local Variables://verilog-library-directories:(".")//End:module test (/*AUTOARG*/ // Outputs douty, // Inputs clk, rst_n, i );input clk;input rst_n; input i;output douty;parameter DWIDTH=32;/*AUTOREG*/// Beginning of automatic regs (for this module's undeclared outputs)reg douty;// End of automatics/*AUTOWIRE*/// Beginning of automatic wires (for undeclared instantiated-module outputs)wire [DWIDTH-1:0] o; // From u_foo of foo.v// End of automaticsassign doutx = i;always @(posedge clk or negedge rst_n)begin if(!rst_n)begin douty <= 1'd0; end else douty <= doutx;endassign doutx = i & o[DWODTH-1];foo u_foo(/*autoinst*/ // Outputs .o (o[DWIDTH-1:0]), // Inputs .i (i));endmodule//Local Variables://verilog-library-directories:("." "foo")//End:module foo(/*AUTOARG*/ // Outputs o, // Inputs i );input i;output [DWIDTH-1:0] o;endmodule//Local Variables://verilog-library-directories:(".")//End://Local Variables://verilog-library-directories:("." "子文件夹名1" "子文件夹名2")//End::!emacs --batch *.v -f verilog-batch-auto

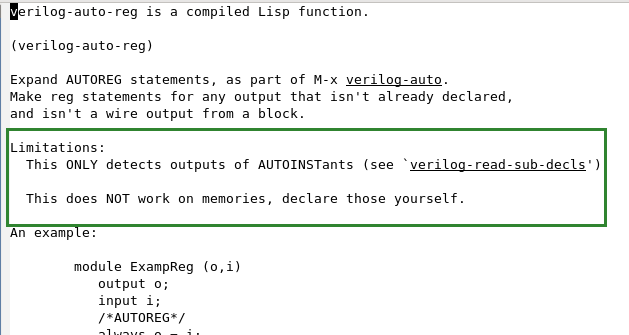

设置第三行执行文件的emacs.exe的路径。这个插件有些小问题,autoinst执行时,如果修改了端口名称,则会恢复到默认。autowire和autoreg,只能对output和实例化的端口进行操作,直接写一个always块或assign,如果操作的变量,不在output或实例化端口中,也不会自动定义。本文开始的那段代码中的变量doutx就没有被自动定义。在Emacs-菜单栏-Verilog-AUTO Help中打开这两个auto的详细介绍,所以读者在使用的过程中应该注意。

设置第三行执行文件的emacs.exe的路径。这个插件有些小问题,autoinst执行时,如果修改了端口名称,则会恢复到默认。autowire和autoreg,只能对output和实例化的端口进行操作,直接写一个always块或assign,如果操作的变量,不在output或实例化端口中,也不会自动定义。本文开始的那段代码中的变量doutx就没有被自动定义。在Emacs-菜单栏-Verilog-AUTO Help中打开这两个auto的详细介绍,所以读者在使用的过程中应该注意。 对于这两个问题,我找到了另外一个插件。

对于这两个问题,我找到了另外一个插件。

Vim官网的插件

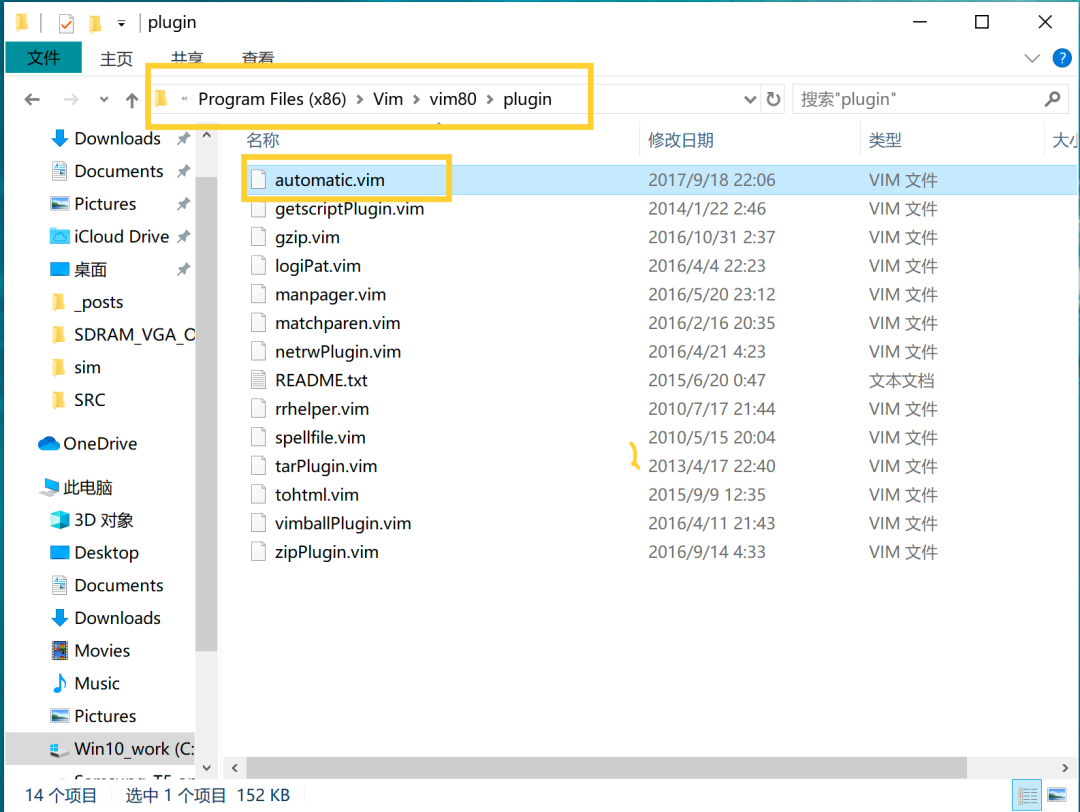

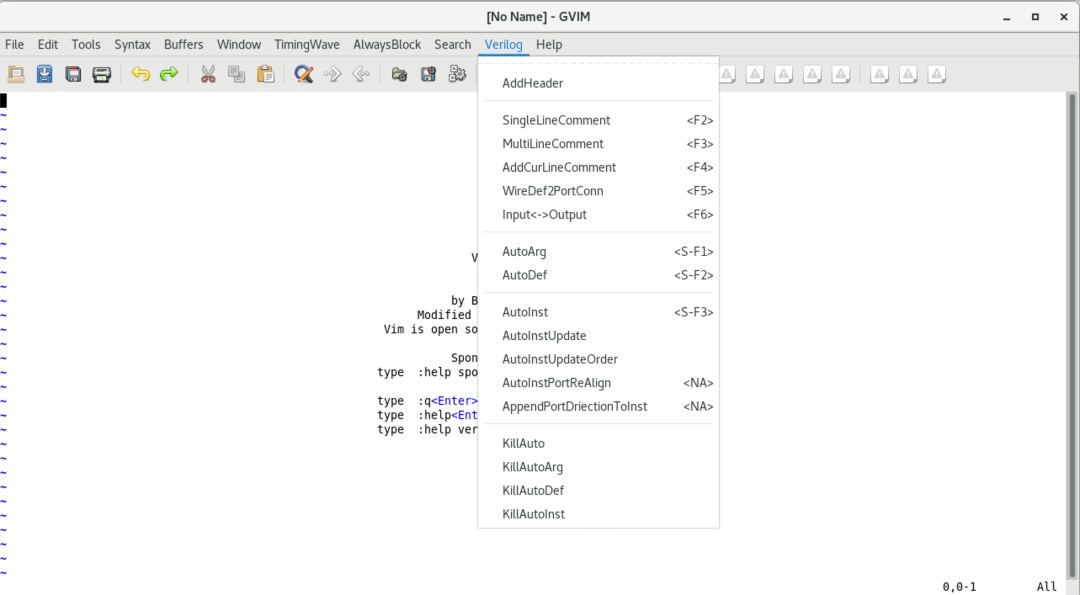

https://www.vim.org/scripts/script.php?script_id=4067直接下载这个文件。在Windows中使用直接放在安装目录下plugin文件夹下,重启Gvim在菜单栏加载插件菜单。 MacOS与CentOS下需要安装这个插件,在用户根目录下新建一个文件夹为.vim/plugin/,然后这个插件复制进去,重新打开Gvim,就可以看到插件自动加载。

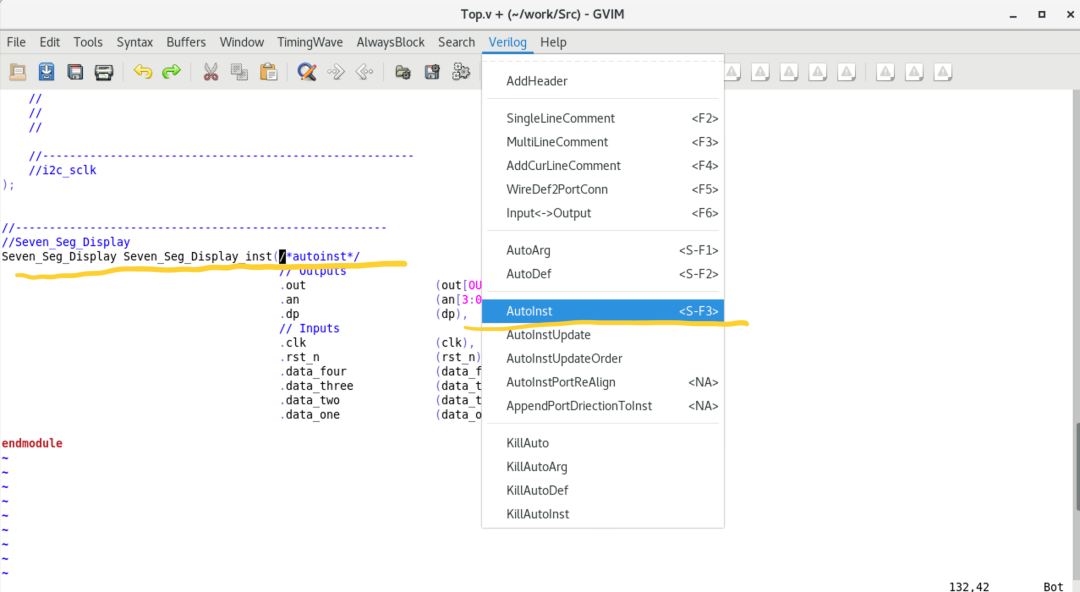

MacOS与CentOS下需要安装这个插件,在用户根目录下新建一个文件夹为.vim/plugin/,然后这个插件复制进去,重新打开Gvim,就可以看到插件自动加载。 autoinst使用的过程中需要注意的是,光标必须放在需要操作位置对应的那一行,然后使用快捷键或者点击菜单栏图形界面就可以直接运行。这个插件的问题是不能垮文件夹实例化,不过对于平时做些小练习绰绰有余了,效率提高100%。

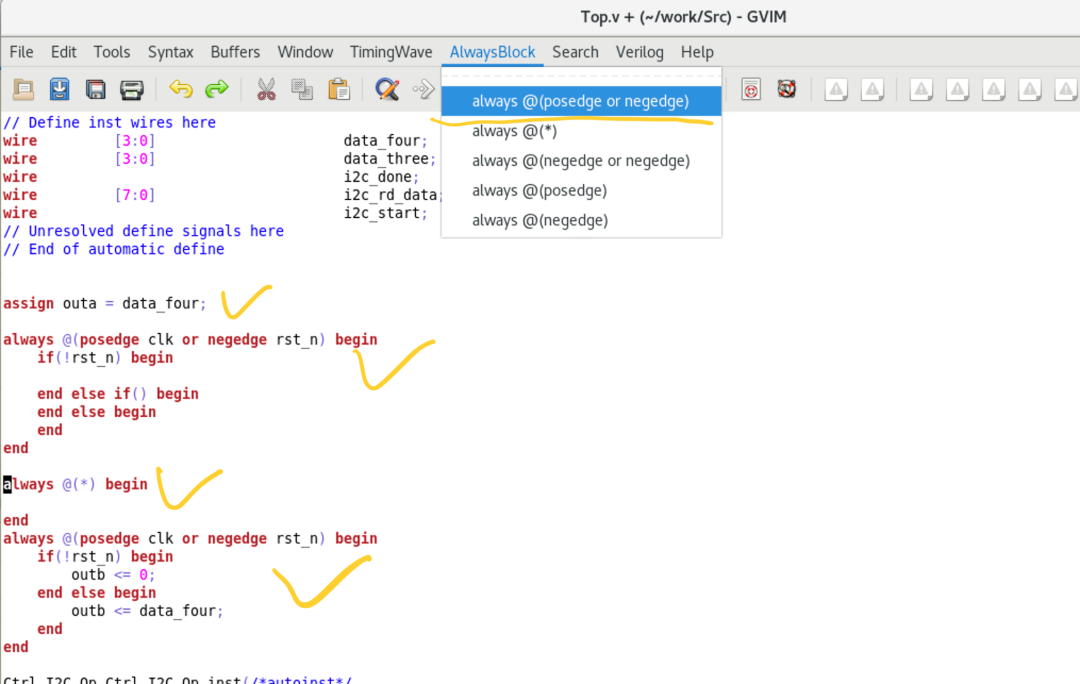

autoinst使用的过程中需要注意的是,光标必须放在需要操作位置对应的那一行,然后使用快捷键或者点击菜单栏图形界面就可以直接运行。这个插件的问题是不能垮文件夹实例化,不过对于平时做些小练习绰绰有余了,效率提高100%。 还可以添加always块,编写代码时,直接写assign和always块给变量进行赋值,使用autodef,则会自动声明变量成对应的wire或者reg。

还可以添加always块,编写代码时,直接写assign和always块给变量进行赋值,使用autodef,则会自动声明变量成对应的wire或者reg。

最后

Emacs verilog-mode只能自动声明输出和实例化端口的变量,而且在Windows平台下,会出现自动对齐参差不齐,但是可以自定义跨文件夹实例化。而automatic.vim弥补了Emacs verilog-mode自动定义功能的不足,但是却没有跨文件夹实例化的功能。所以两个可以配合着用,对于做个小练习,甚至做工程开发也完全没有问题。最常用的就这几个功能,还有其他功能读者可以自己去尝试,提高编码效率。最后,编辑器这个东西,找个自己用的顺的,能跨多个平台的,多人协作尽量保持统一的就行了。没有最好,只有最适合你的。

更多推荐

已为社区贡献4条内容

已为社区贡献4条内容

所有评论(0)